## Study of Reliable Timing System at KEK Accelerator Complex

Author: Supervisor:

Di Wang Prof. Furukawa Kazuro

DOCTOR OF PHILOSOPHY

Department of Accelerator Science School of High Energy Accelerator Science The Graduate University for Advanced Studies, SOKENDAI

September 2021

## Declaration of Authorship

I, Di Wang, declare that this thesis titled, 'Study of Reliable Timing System at KEK Accelerator Complex' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: Di Wang  |  |  |

|------------------|--|--|

|                  |  |  |

| Date: June, 2021 |  |  |

A dissertation submitted to Department of Accelerator Science,

School of High Energy Accelerator Science,

The Graduate University for Advanced Studies, SOKENDAI,

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

#### **Advisory Committee**

| 1. | Prof.Obina | Takashi | KEK. |

|----|------------|---------|------|

|    |            |         |      |

2. Prof.Kamikubota Norihiko KEK

3. Assoc.Prof.Kobayashi Tetsuya KEK

4. Assoc.Prof.Satoh Masanori KEK

5. Prof.Furukawa Kazuro KEK

6. Prof.Masuda Takemasa Japan Synchrotron Radiation Research

Institute

#### Abstract

School of High Energy Accelerator Science

Department of Accelerator Science

Doctor of Philosophy

#### Study of Reliable Timing System at KEK Accelerator Complex

by Di Wang

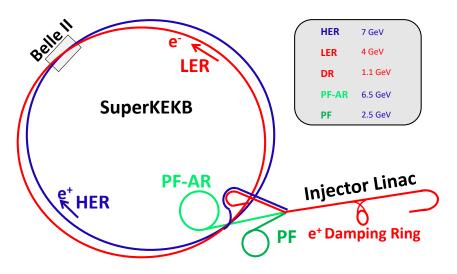

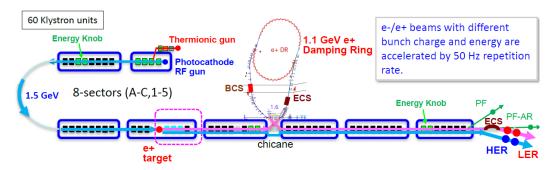

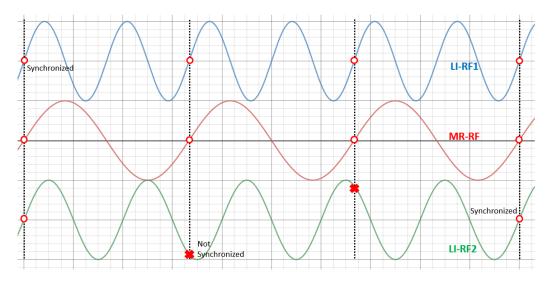

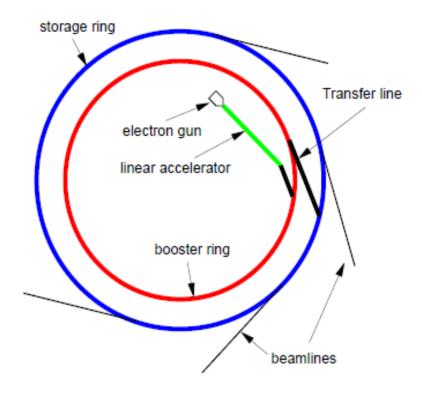

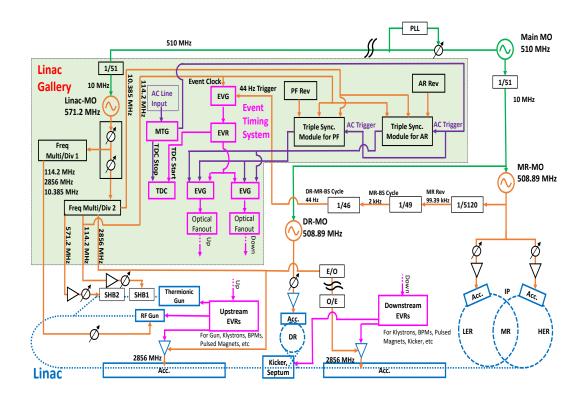

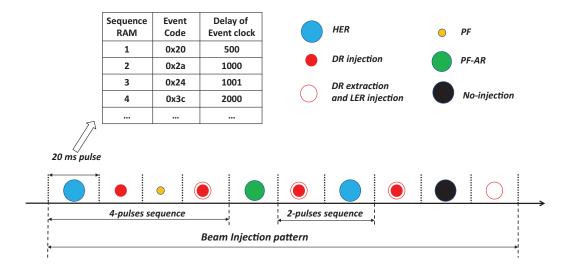

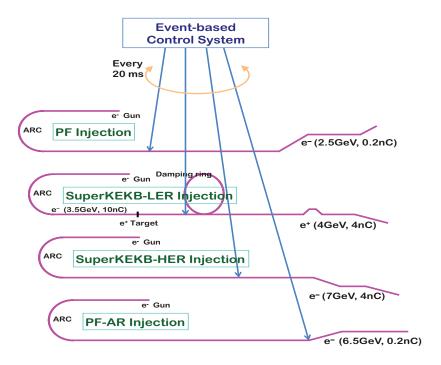

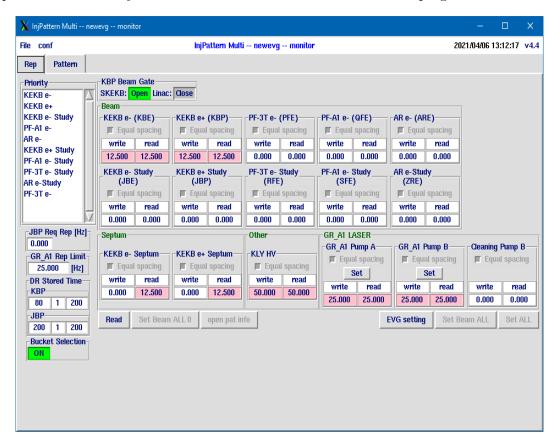

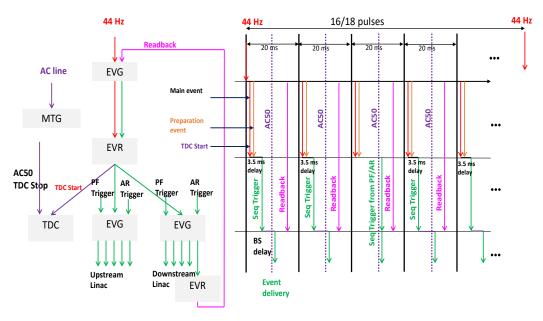

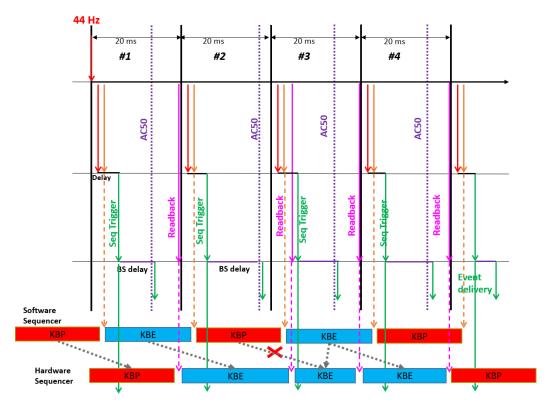

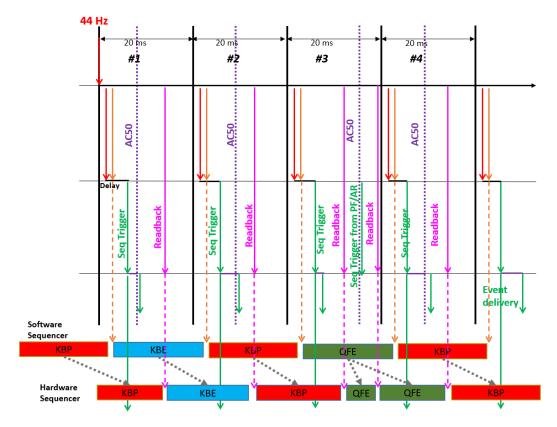

The timing system provides high-precision signals to control a variety of hardware and software in the accelerator complex. At KEK, the timing system at injector linear accelerator (LINAC) is responsible for RF frequency synchronization between two SuperKEKB main rings (MR) and LINAC, trigger delivery, and bucket selection process. The LINAC timing system also provides trigger signals for two light source rings (PF/PF-AR) simultaneously, which demanding the timing system handle the injection procedure for 4 rings at 50 Hz. The beam properties and device control parameters are modulated every pulse through the timing system.

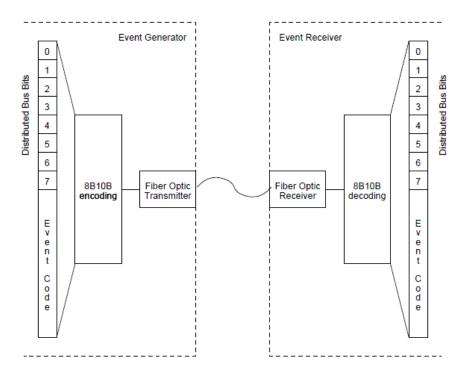

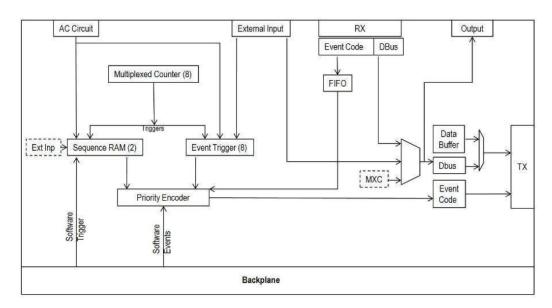

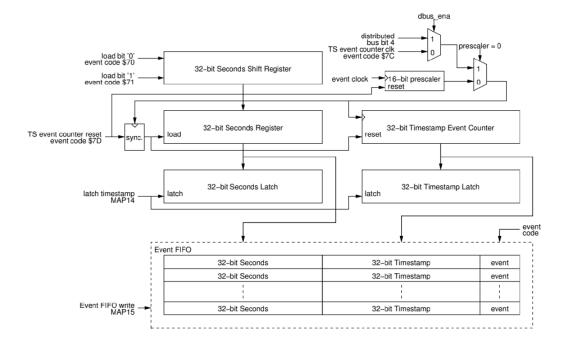

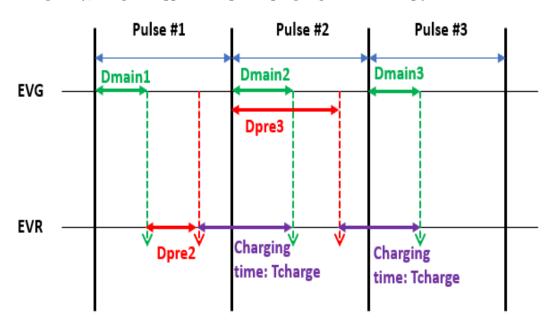

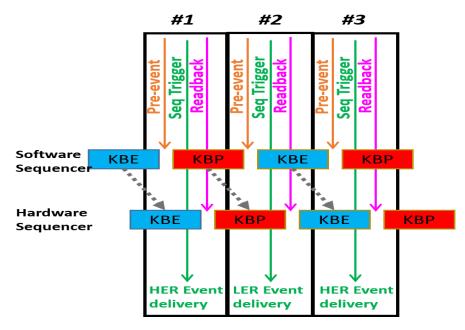

The event-based timing system generates event codes in an event generator (EVG) and distributes these event codes in a scheduled delay time to all local event receivers (EVR). The EVR module equips with the pulse generation circuit with variable pulse delay and width to supply trigger signals for hardware upon receiving the desired event code.

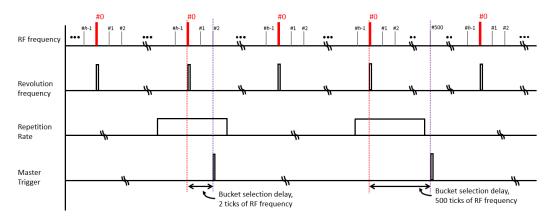

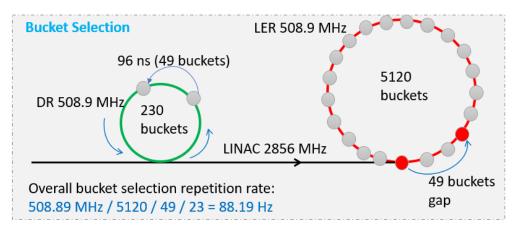

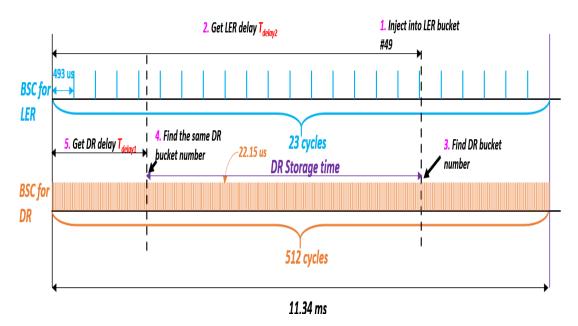

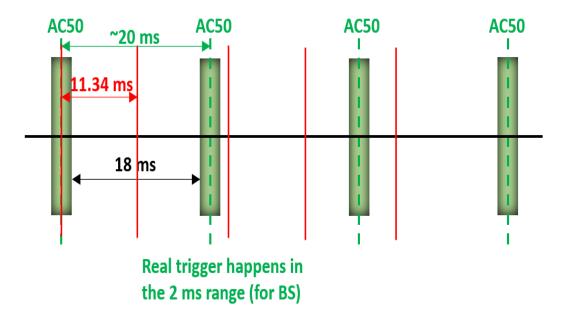

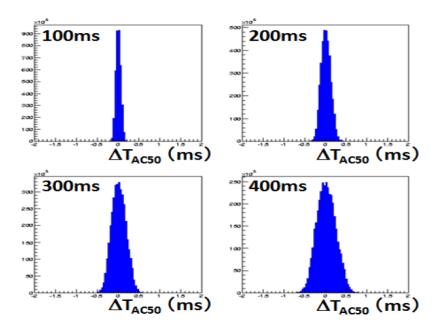

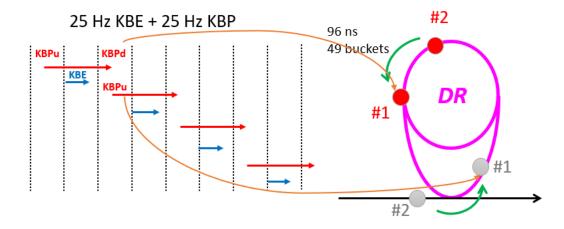

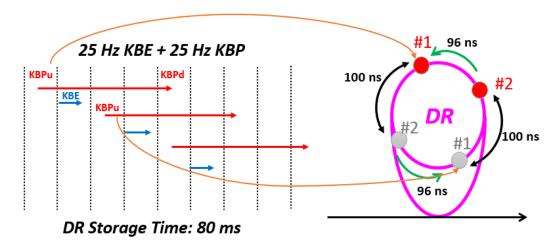

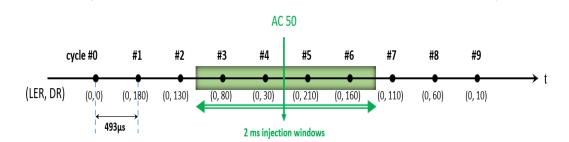

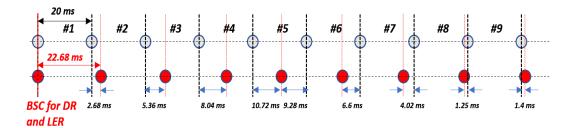

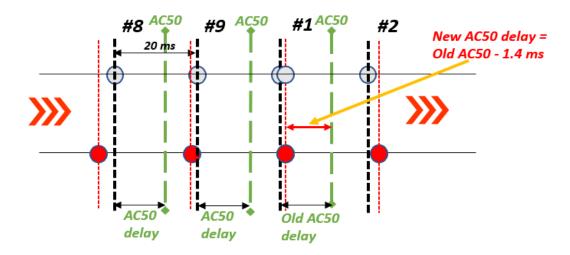

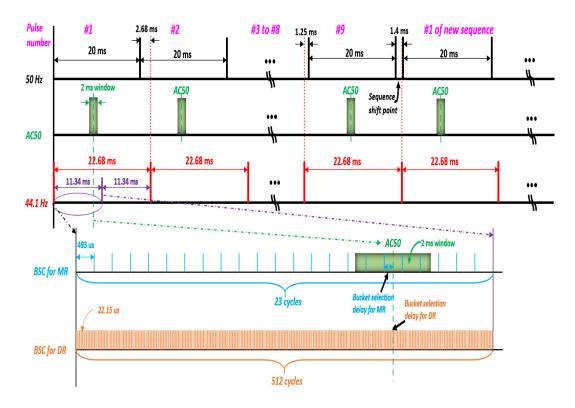

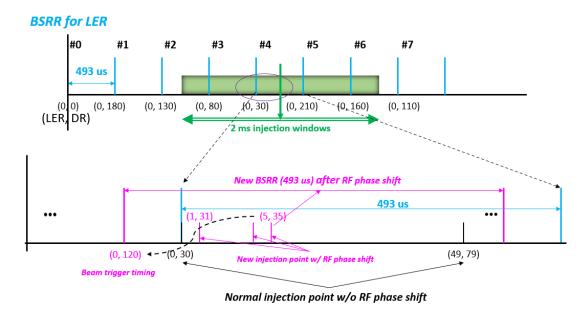

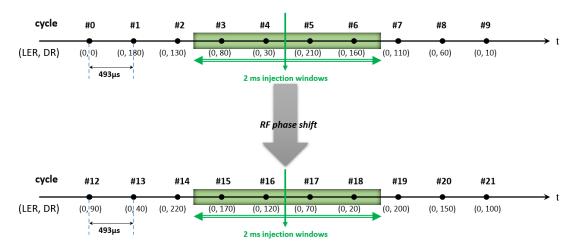

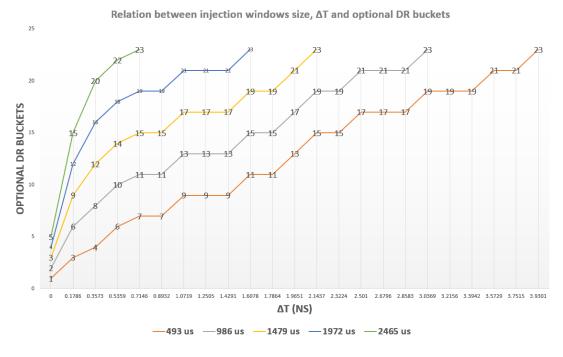

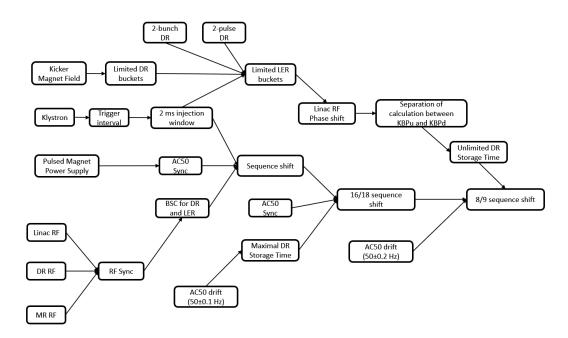

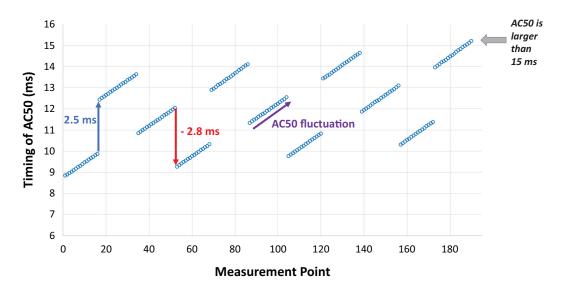

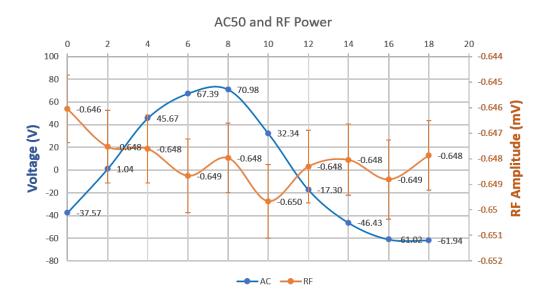

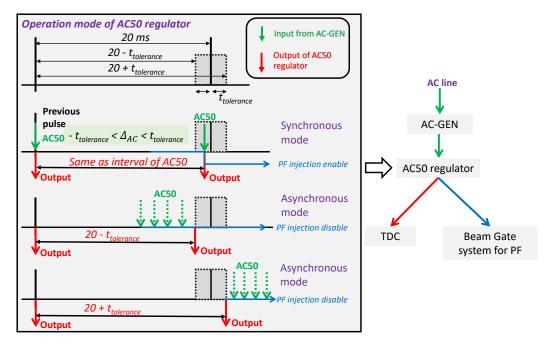

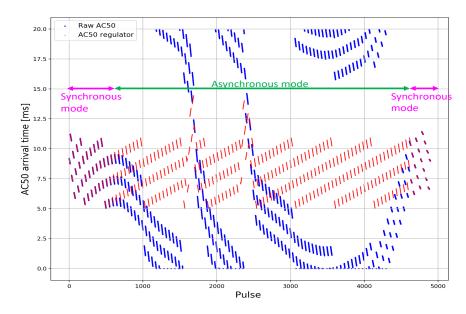

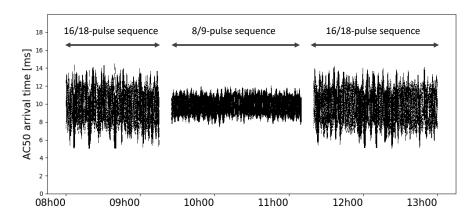

Several constraints from hardware must be considered during the design of the timing system. Some devices, like pulsed magnet power supply, need to be triggered at the same phase of the 50 Hz AC (AC50) power line to maintain a stable operation. Thus, the timing system operates under the AC50-dependent mode. On the other hand, the high-power klystron modulator needs at least 18 ms to accumulate power for klystron which results in a trigger interval restriction for consecutive injection pulse. The bucket selection cycle (BSC) is defined as a period that can select all the RF buckets inside a ring. The BSC for SuperKEKB electron beam injection is 493  $\mu$ s which is effortless to synchronize with AC50 in 50 Hz. However, a newly constructed positron damping ring (DR) to lower the positron beam emittance enlarges the bucket selection period for a whole DR-MR cycle. The RF bucket number for DR and MR are 230 and 5120, respectively. The BSC for SuperKEKB positron beam injection becomes 23 times longer

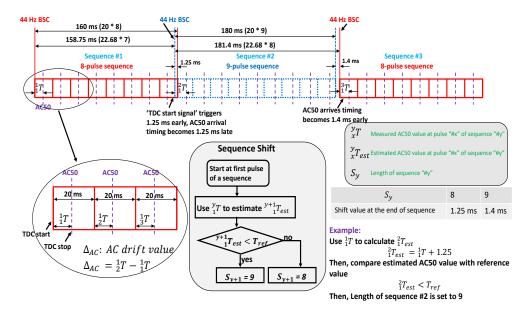

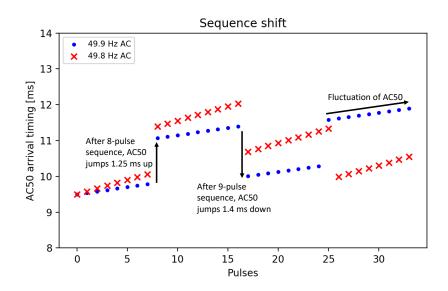

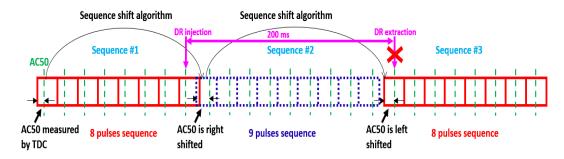

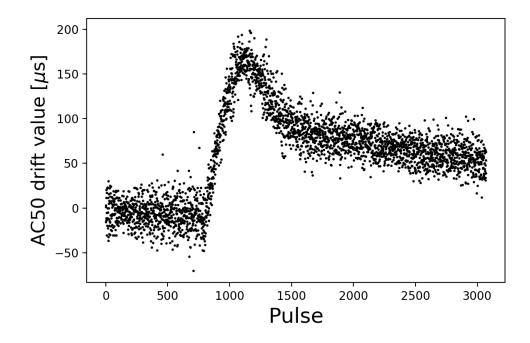

(i.e., 11.34 ms) due to DR operation and the synchronization between BSC and AC50 in every pulse is broken. The AC line always fluctuates due to requirements from the power company. Consequently, a method called "sequence shift" is implemented to synchronize with both AC50 and BSC for positron as well as compensating for the AC line fluctuation. The length of the sequence and how the sequence shift is accomplished are described in detail.

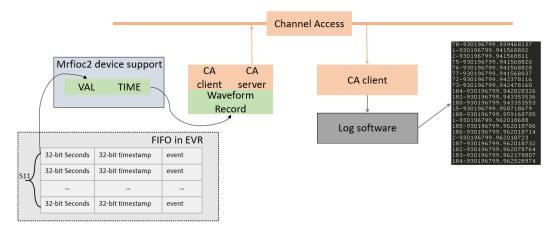

Apart from the triggering function of a timing system, several significant features are also utilized to either meet the hardware requirement or improve the functionality of the timing system. The beam gate system provides a highly flexible way to disable the trigger delivery to specific devices, such as electron guns or DR injection and extraction magnet, without stopping the operation of EVG. The data buffer component contributes to the auxiliary data delivery, like beam mode, pulse ID, or bucket number information, other than normal trigger signal delivery.

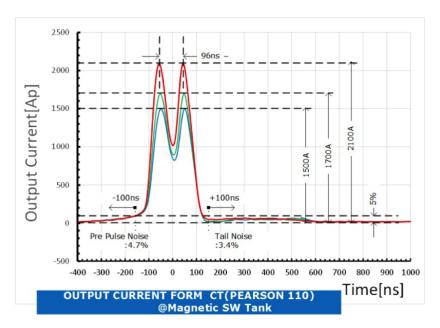

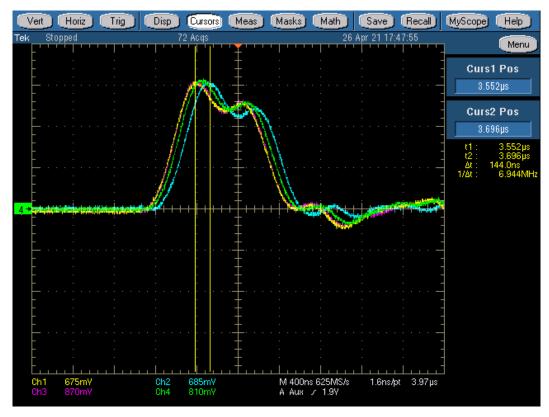

Another limit of the numbers of selectable MR RF buckets for the 2-bunch and 2-pulse operation comes from the rising time of the DR kicker magnet field. To overcome this disadvantage, the RF phase in the downstream LINAC is modulated every pulse to increase the coincidence opportunity between DR RF and LINAC RF. The RF phase shift also brings time discrepancy of nanosecond scale between timing trigger and beam trigger. The beam behavior under such discrepancy is investigated to assure that the beam quality variation is acceptable for the SuperKEKB physics run. By means of the pulse-to-pulse RF phase modulation, all MR RF buckets can be selected in one pulse even during 2-bunch and 2-pulse operations.

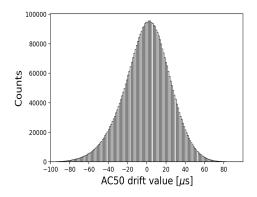

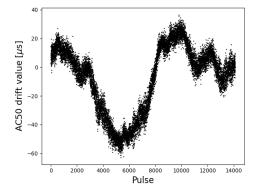

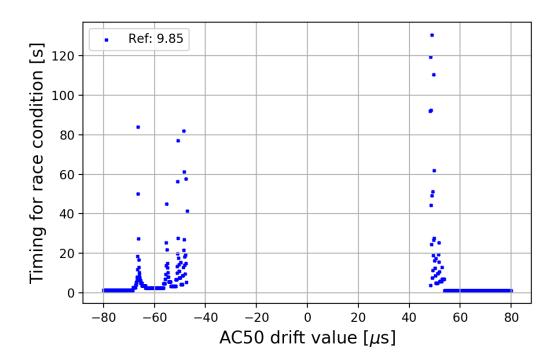

The effort of establishing a reliable timing system at LINAC and several solutions to improve the system's robustness are presented in this work. During the commissioning of SuperKEKB, the beam error originates from the timing system was observed. This work mainly focuses on the failure mode analysis of the timing system at LINAC. We follow the procedure of failure mode analysis to understand the failure mode, identify the failure cause, and propose solutions. Several log systems for quickly diagnosing the complex system are built and tested. With the help of the log system, two failure modes called "beam mode replacement" and "redundant beam mode" are comprehensively analyzed and their failure causes are identified. The error can be categorized into two parts, the systematic error caused by either software bug or problematic system design, and the unexpected error caused by strong AC50 drift.

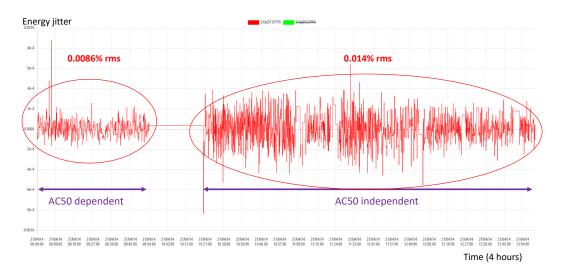

Several possibilities for solutions are discussed in this work. One solution is to remove the AC50 trigger dependency. A beam experiment is done by examining the beam quality degradation under the AC50-independent mode. According to the beam experiment, the AC50-independent operation is acceptable for SuperKEKB MR whereas not feasible

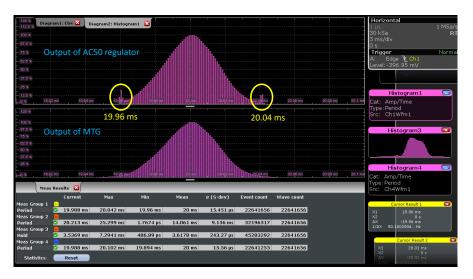

for PF injection due to the strong relationship between the power supply of the PF injection kicker magnet and AC50. Partially AC50-dependent operation mode is proposed by switching between the AC50-independent mode and AC50-dependent mode. Consequently, an AC50 regulator module is installed in the timing system to mask the strong AC50 drift and provide signals within  $50\pm0.1~\mathrm{Hz}$  to stabilize the timing system. A detailed analysis of the process logic and performance of the AC50 regulator module is represented in this thesis. Another possibility is to decrease the sequence length to mitigate the AC50 drift effect. The DR storage time becomes significant because both DR injection and extraction timing need to synchronize with AC50. The injection timing and extraction timing are strongly related without downstream LINAC RF phase shift. Thus, either decreasing the DR storage time or decoupling the DR injection and extraction pulse will allow us to shorten the sequence length. An improvement of the sequence shift algorithm is also necessary to handle some extremely strong AC50 drift situations. An example is given to illustrate how the sequence shift with considering recent AC drift value can increase the stability of the timing system.

### Acknowledgements

Many talented and amiable people shared their knowledge and helped form my thinking in this thesis. First and foremost, I want to thank my esteemed supervisors, Dr. Kazuro Furukawa and Dr. Masanori Satoh, who patiently gave me advices and recommendations to pursue interesting and significant problems in my area. The classes they taught provide not only invaluable insight of the historical evolution of accelerator control system but also the philosophy of phronesis on practical obstacle.

I am deeply grateful to Dr. Hiroshi Kaji, Dr. Hitoshi Sugimura, Dr. Fusashi Miya-HARA and Dr. Yoshinori Enomoto for their insightful comments and suggestions at every stage of the research project.

I would like to offer my special thanks to Dr. Tetsuo Shidara, Dr. Hiroyasu Ego, Dr. Takuya Natsui and Dr. Takako Miura for their kindly help on detailed explanation and test bench construction during my klystron experiment.

I have also benefitted from conversations with Mr. Yuichi IITSUKA, Mr. Takuya KUDOU, Mr. Shiro KUSANO, Mr. Hideki SAOTOME and many other staffs during the software programming and hardware debugging.

My leisure life in Japan becomes pleasing, satisfactory and cheerful with the help of my colleagues, Dr. Baiting Du, Dr. Na Liu, Dr. M.A. Rehman, Mrs. Min Yang, Mr. Ce Zhang, Mr. Yao Lu and Mr. Yuki Abe.

Last but not least, I want to thank all the open knowledge organizations, such as the Wikimedia Foundation and the Free Software Foundation, whose principles and methodologies are knowledge acquirement is a basic human-rights. What they pursue inspires me to insist on the belief of the existence of common good for all human.

## Contents

| D  | eclar                           | ation of Authorship                   | ii                    |

|----|---------------------------------|---------------------------------------|-----------------------|

| A  | bstra                           | et                                    | ii                    |

| A  | cknov                           | vledgements                           | $\mathbf{v}$          |

| C  | onter                           | $\mathbf{t}\mathbf{s}$                | ii                    |

| Li | st of                           | Figures                               | κi                    |

| Li | st of                           | Tables                                | $\mathbf{v}$          |

| A  | bbre                            | riations xv                           | ii                    |

| 1  | Intr                            | $\operatorname{oduction}$             | 1                     |

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | EPICS                                 | 1<br>3<br>5<br>7<br>8 |

| 2  |                                 |                                       | 1                     |

|    | $\frac{2.1}{2.2}$               |                                       | 1                     |

|    | 2.2                             |                                       | 5                     |

|    |                                 |                                       | 6                     |

|    |                                 |                                       | 8                     |

|    | 2.3                             | 1 0                                   | 9                     |

|    |                                 |                                       | 0.0                   |

|    |                                 |                                       | 1                     |

|    |                                 |                                       | 1                     |

|    |                                 | 2.3.4 Event Codes Generation          | 2                     |

|    |                                 |                                       | 2                     |

|    |                                 | 2.3.6 Event Sequencer                 | 4                     |

|    | 2.4                             | TBTS                                  | 4                     |

|    | 2.5                             | Evamples of Accelerator Timing system | 5                     |

*Contents* viii

|   |     | 2.5.1         | BEPC II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25        |

|---|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |     | 2.5.1 $2.5.2$ | SLS Timing System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

|   |     | 2.0.2         | DDS Tilling System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20        |

| 3 | Ove | erview        | of Timing System at KEK LINAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29        |

|   | 3.1 |               | vare and Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29        |

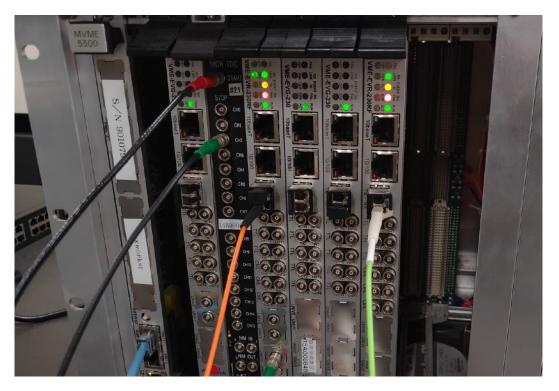

|   |     | 3.1.1         | Event Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30        |

|   |     | 3.1.2         | MTG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   |     | 3.1.3         | TDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|   |     | 3.1.4         | RFM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35        |

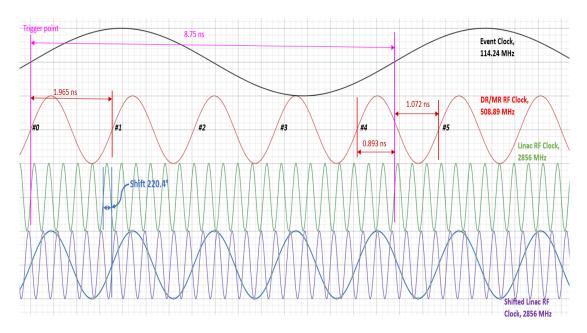

|   | 3.2 |               | rnchronization at LINAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36        |

|   | 3.3 |               | t Selection for SuperKEKB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38        |

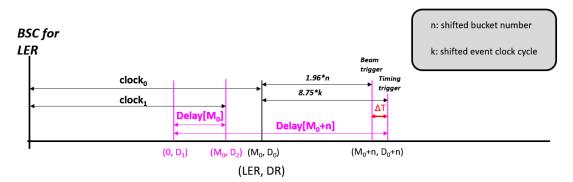

|   |     | 3.3.1         | Delay Calculation of RF Buckets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38        |

|   |     | 3.3.2         | Decision Making of Injection Bucket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41        |

|   |     | 3.3.3         | Constituents of Bucket Selection System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44        |

|   | 3.4 |               | Gate Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 0.1 | Deam          | Guite Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10        |

| 4 | Rec | quirem        | ent of Timing System at KEK LINAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>47</b> |

|   | 4.1 | PPM           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47        |

|   |     | 4.1.1         | Simultaneous Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48        |

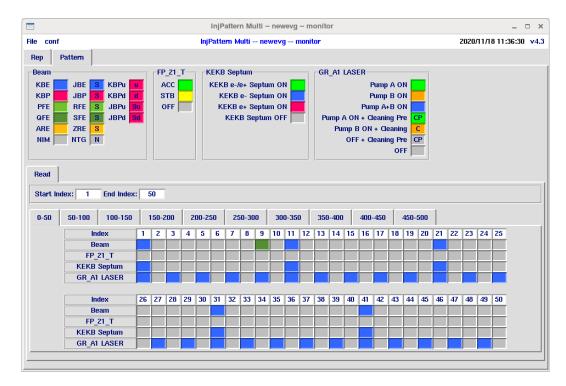

|   |     | 4.1.2         | Beam Mode and Injection Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49        |

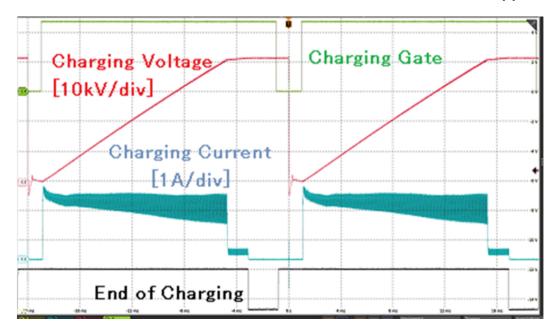

|   |     | 4.1.3         | Dependency between Pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52        |

|   | 4.2 | AC50          | Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53        |

|   | 4.3 | DR O          | peration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55        |

|   |     | 4.3.1         | Dependency between Injection and Extraction Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55        |

|   |     | 4.3.2         | DR Storage Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56        |

|   |     | 4.3.3         | 2-bunch and 2-pulse operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57        |

|   |     |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| 5 | _   |               | tation of Timing System at KEK LINAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63        |

|   | 5.1 | Seque         | nce Shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|   |     | 5.1.1         | 8/9 Pulses Sequence Shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

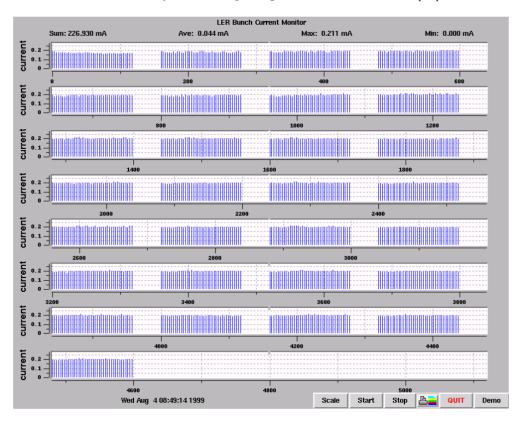

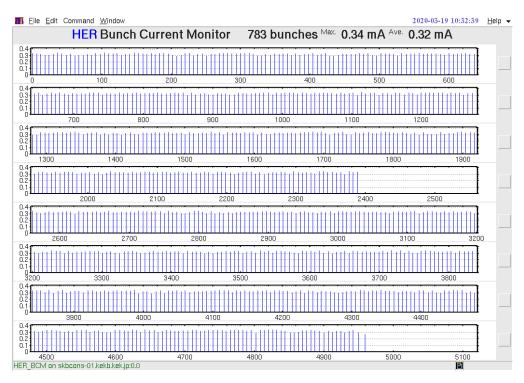

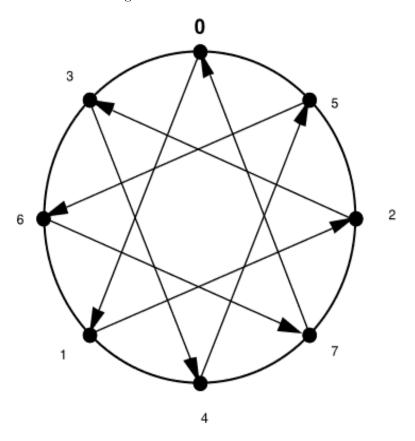

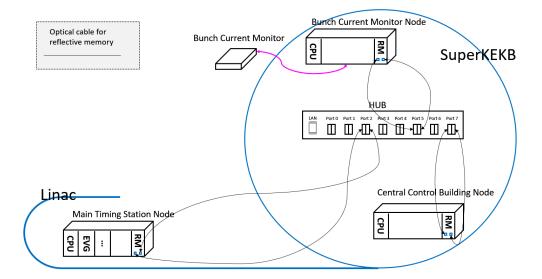

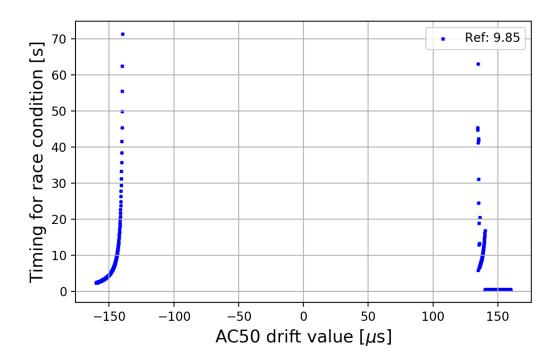

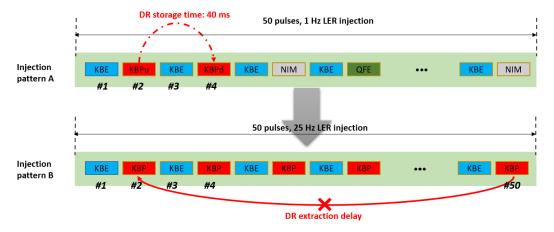

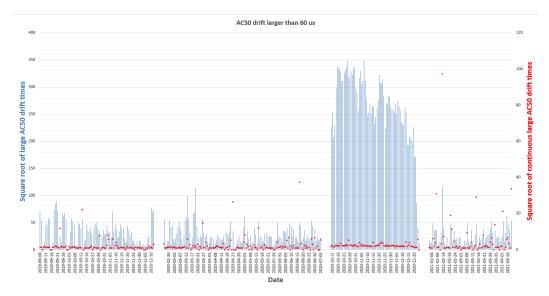

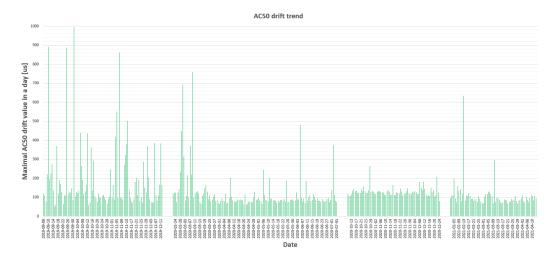

|   |     | 5.1.2         | Sequence Shift Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |